# **Hammer**

Release 1.0.0

**Berkeley Architecture Research**

## **CONTENTS:**

| 1 | Ham | mer Bas | ics                            | 3 |

|---|-----|---------|--------------------------------|---|

|   | 1.1 | Hamme   | er Overview                    | 3 |

|   |     | 1.1.1   | Main Hammer                    | 3 |

|   |     | 1.1.2   | Tech Plugins                   | 4 |

|   |     | 1.1.3   | Tool Plugins                   | 4 |

|   |     | 1.1.4   | Calling Hammer                 | 5 |

|   |     | 1.1.5   | Summary                        | 5 |

|   | 1.2 | Hamme   | er Setup                       | 6 |

|   |     | 1.2.1   | User Setup                     | 6 |

|   |     | 1.2.2   | Developer Setup                | 7 |

|   | 1.3 | Migrati | on Guide                       | 0 |

|   |     | 1.3.1   | Selecting Plugins              | 1 |

|   |     | 1.3.2   | import Statements              | 1 |

|   |     | 1.3.3   | Technology JSON                | 1 |

|   |     | 1.3.4   | Plugin File Structure          | 2 |

|   |     | 1.3.5   | Resource Files                 | 3 |

|   |     | 1.3.6   | pyproject.toml                 | 3 |

|   |     |         |                                | _ |

| 2 |     |         | hnology Plugins 19             |   |

|   | 2.1 |         | er Technologies                |   |

|   | 2.2 | 2.1.1   | HammerTechnology Class         | _ |

|   | 2.2 |         | er Tech JSON                   |   |

|   |     | 2.2.1   | Technology Install             |   |

|   |     | 2.2.2   | DRC/LVS Deck Setup             |   |

|   |     | 2.2.3   | Library Setup                  |   |

|   |     | 2.2.4   | Stackup                        |   |

|   |     | 2.2.5   | Sites                          |   |

|   |     | 2.2.6   | Special Cells                  |   |

|   |     | 2.2.7   | Don't Use, Physical-Only Cells |   |

|   | 2.2 | 2.2.8   | Full Schema                    |   |

|   | 2.3 |         | er Tech defaults.yml           |   |

|   | 2.4 |         | Technology Library             |   |

|   |     | 2.4.1   | PDK Setup                      |   |

|   |     | 2.4.2   | SRAM Macros                    |   |

|   |     | 2.4.3   | NDA Files                      |   |

|   |     | 2.4.4   | Resources                      |   |

|   |     | 2.4.5   | Manual PDK Setup               |   |

|   | 2.5 |         | Technology Library             |   |

|   |     | 2.5.1   | Setup and Environment          |   |

|   |     | 2.5.2   | Dummy SRAMs                    | 3 |

|   | 2.6 | _              | Known Issues                    | 33<br>34 |

|---|-----|----------------|---------------------------------|----------|

|   |     | 2.6.1<br>2.6.2 | Dummy SRAMs                     | 34<br>34 |

| 3 |     |                | l Plugins                       | 35       |

|   | 3.1 |                | er CAD Tools                    | 35       |

|   | 3.2 | _              | up a Hammer CAD Tool Plugin     | 35       |

|   |     | 3.2.1          | Tool Class                      | 36       |

|   |     | 3.2.2          | Steps                           | 36       |

|   |     | 3.2.3          | Getting Settings                | 36       |

|   |     | 3.2.4          | Writing TCL                     | 36       |

|   |     | 3.2.5          | Executing the Tool              | 36       |

|   |     | 3.2.6          | Tool Outputs                    | 36       |

|   |     | 3.2.7          | defaults.yml                    | 37       |

|   | 3.3 | OpenR          | OAD Place-and-Route Tool Plugin | 37       |

|   |     | 3.3.1          | Tool Setup                      | 37       |

|   |     | 3.3.2          | Tool Steps                      | 37       |

|   |     | 3.3.3          | Step Details                    | 38       |

|   |     | 3.3.4          | Issue Archiving                 | 38       |

| 4 | Ham | mer Flo        |                                 | 41       |

|   | 4.1 | Hamm           | er Actions                      | 41       |

|   | 4.2 | Synthe         | sis                             | 41       |

|   |     | 4.2.1          | Synthesis Setup Keys            | 41       |

|   |     | 4.2.2          | Synthesis Input Keys            | 42       |

|   |     | 4.2.3          | Synthesis Inputs                | 42       |

|   |     | 4.2.4          | Synthesis Outputs               | 42       |

|   |     | 4.2.5          | Synthesis Commands              | 42       |

|   | 4.3 |                | nd-Route                        | 43       |

|   |     | 4.3.1          | P&R Setup Keys                  | 43       |

|   |     | 4.3.2          | P&R Input Keys                  | 43       |

|   |     | 4.3.3          | P&R Inputs                      | 44       |

|   |     | 4.3.4          | P&R Outputs                     | 44       |

|   |     | 4.3.5          | P&R Commands                    | 44       |

|   | 4.4 | DRC            |                                 | 44       |

|   |     | 4.4.1          | DRC Setup Keys                  | 45       |

|   |     | 4.4.2          | DRC Input Keys                  | 45       |

|   |     | 4.4.3          | DRC Inputs                      | 45       |

|   |     | 4.4.4          | DRC Outputs                     | 45       |

|   |     | 4.4.5          | DRC Commands                    | 45       |

|   | 4.5 | LVS .          |                                 | 46       |

|   |     | 4.5.1          | LVS Setup Keys                  | 46       |

|   |     | 4.5.2          | LVS Input Keys                  | 46       |

|   |     | 4.5.3          | LVS Inputs                      | 46       |

|   |     | 4.5.4          | LVS Outputs                     | 46       |

|   |     | 4.5.5          | LVS Commands                    | 47       |

|   | 4.6 | Simula         |                                 | 47       |

|   |     | 4.6.1          | Simulation Setup Keys           | 47       |

|   |     | 4.6.2          | Simulation Input Keys           | 47       |

|   |     | 4.6.3          | Simulation Inputs               | 49       |

|   |     | 4.6.4          | Simulation Outputs              | 49       |

|   |     | 4.6.5          | Simulation Commands             | 49       |

|   | 4.7 | Power          |                                 | 49       |

|   |                 | 4.7.1   | Power Setup Keys                           | 50 |

|---|-----------------|---------|--------------------------------------------|----|

|   |                 | 4.7.2   | Simulation Input Keys                      | 50 |

|   |                 | 4.7.3   | Power Inputs                               | 51 |

|   |                 | 4.7.4   | Power Outputs                              | 51 |

|   |                 | 4.7.5   | Power Commands                             | 51 |

|   | 4.8             | Formal  | Verification                               | 52 |

|   |                 | 4.8.1   | Formal Verification Setup Keys             | 52 |

|   |                 | 4.8.2   | Formal Verification Input Keys             |    |

|   |                 | 4.8.3   | Formal Verification Inputs                 |    |

|   |                 | 4.8.4   | Formal Verification Outputs                |    |

|   |                 | 4.8.5   | Formal Verification Commands               |    |

|   | 4.9             |         | Ciming Analysis                            |    |

|   |                 | 4.9.1   | STA Setup Keys                             |    |

|   |                 | 4.9.2   | STA Input Keys                             |    |

|   |                 | 4.9.3   | STA Inputs                                 |    |

|   |                 | 4.9.4   | STA Outputs                                |    |

|   |                 | 4.9.5   | STA Commands                               |    |

|   |                 | 4.7.5   | Unit Communities                           | 33 |

| 5 | Ham             | mer Use | <u> </u>                                   | 57 |

|   | 5.1             |         | er IR and Meta Variables                   | 57 |

|   |                 | 5.1.1   | Hammer IR                                  |    |

|   |                 | 5.1.2   | The hammer-config library                  |    |

|   |                 | 5.1.3   | Basics                                     |    |

|   |                 | 5.1.4   | Overriding                                 |    |

|   |                 | 5.1.5   | Meta actions                               |    |

|   |                 | 5.1.6   | Applying multiple meta actions             |    |

|   |                 | 5.1.7   | Common meta actions                        |    |

|   |                 | 5.1.8   | Type Checking                              |    |

|   |                 | 5.1.9   | Key History                                |    |

|   |                 | 5.1.10  | Key Description Lookup                     |    |

|   |                 | 5.1.11  | Reference                                  |    |

|   | 5.2             | Hamme   |                                            |    |

|   | 3.2             | 5.2.1   | Power Specification                        |    |

|   |                 | 5.2.2   | Timing Constraints                         |    |

|   |                 | 5.2.3   | Floorplan & Placement                      |    |

|   |                 | 5.2.4   | Bumps                                      |    |

|   |                 | 5.2.5   | Pins                                       |    |

|   |                 | 5.2.6   | Power Straps                               |    |

|   |                 | 5.2.7   | Special Cells                              |    |

|   |                 | 5.2.8   | Submission                                 |    |

|   | 5.3             |         | ontrol                                     |    |

|   | 5.5             | 5.3.1   | Command-line Interface                     |    |

|   | 5.4             |         | ing Hammer with Hooks                      |    |

|   | J. <del>T</del> | 5.4.1   | Hook Methods                               |    |

|   |                 | 5.4.2   | Including Hooks                            |    |

|   |                 | 5.4.3   | Technology, Tool, and User-Provided Hooks  |    |

|   | 5.5             |         | er Buildfile                               |    |

|   | 5.6             |         | hical Hammer Flow                          |    |

|   | 5.0             | 5.6.1   |                                            |    |

|   |                 | 5.6.2   | Hierarchical Hammer Config                 |    |

|   |                 | 5.6.3   | Flow Management and Actions                |    |

|   |                 |         | Cadence Implementation                     |    |

|   |                 | 5.6.4   | Tips for Constraining Hierarchical Modules |    |

|   |                 | 5.6.5   | Special Notes & Limitations                | 76 |

| 6 | Ham   | nmer Examples                | <b>79</b> |

|---|-------|------------------------------|-----------|

|   | 6.1   | End-to-End Integration Tests | 79        |

|   | 6.2   | OpenROAD and Sky130          | 79        |

|   |       | 6.2.1 Instructions           | 79        |

| 7 | Indio | ices and tables              | 81        |

Hammer is a physical design framework that wraps around vendor specific technologies and tools to provide a single API to create ASICs. Hammer allows for reusability in ASIC design while still providing the designers leeway to make their own modifications.

Hammer (Highly Agile Masks Made Effortlessly from RTL) is a framework for building physical design generators for digital VLSI flows. It is an evolving set of APIs that enable reuse in an effort to speed up VLSI flows, which have traditionally been entirely rebuilt for different projects, technologies, and tools.

Hammer is able to generate scripts and collateral for a growing range of CAD tools while remaining technology-agnostic using a well-defined set of common APIs. Tool- and technology-specific concerns live inside plugins, implement APIs, and provide a set of working default configurations.

The vision of Hammer is to reduce the cycle time on VLSI designs, enabling rapid RTL design space exploration and allowing a designer to investigate the impact of various parameters like timing constraints and floorplans without needing to worry about low-level details.

For high-level details about Hammer's design principles and capabilities, please refer to our DAC 2022 paper entitled Hammer: A Modular and Reusable Physical Design Flow Tool. We kindly request that this paper be cited in any publications where Hammer was used.

CONTENTS: 1

2 CONTENTS:

**CHAPTER**

ONE

### **HAMMER BASICS**

This documentation will give an overview of Hammer, its basic setup, its components, and its structure, as well as some typical project setup.

## 1.1 Hammer Overview

Hammer has a set of actions and automatically takes the output of one action and converts it into the input for another. For instance, a synthesis action will output a mapped verilog file which will then automatically by piped to the place-and-route input when a place-and-route action is called.

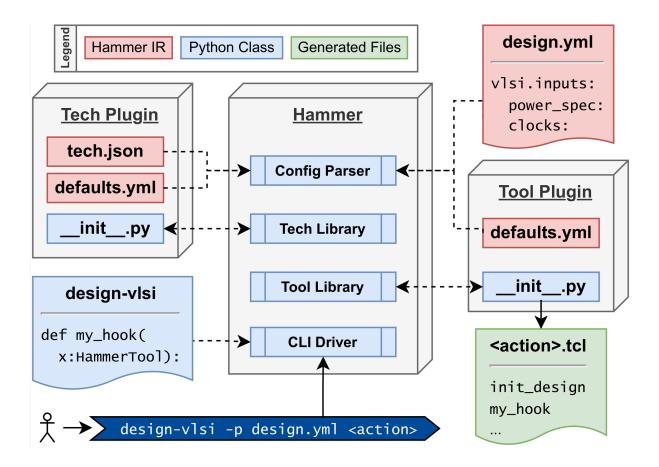

A user's Hammer environment is typically separated into four different components: core Hammer, one or more tool plugins, a technology plugin, and a set of project-specific Hammer input files. Hammer is meant to expose a set of generalized APIs that are then implemented by tool- and technology-specific plugins.

Hammer is included in a larger project called Chipyard which is the unified repo for an entire RTL, simulation, emulation, and VLSI flow from Berkeley Architecture Research. There is an in-depth Hammer demo there, and it is a great place to look at a typical Hammer setup.

#### 1.1.1 Main Hammer

Hammer provides the Python backend for a Hammer project and exposes a set of APIs that are typical of modern VLSI flows. These APIs are then implemented by a tool plugin and a technology plugin of the designer's choice. The structure of Hammer is meant to enable re-use and portability between technologies.

Hammer takes its inputs and serializes its state in the form of YAML and JSON files. The designer sets a variety of settings in the form of keys in different namespaces that are designated in Hammer to control its functionality. These keys are contained in hammer/hammer/config/defaults.yml. This file shows all of the keys that are a part of main Hammer and provides sensible defaults that may be overridden or are set to null if they must be provided by the designer.

Here is an example of a snippet that would be included in the user's input configuration.

```

vlsi.core.technology: "asap7"

vlsi.inputs.supplies:

VDD: "0.7 V"

GND: "0 V"

```

This demonstrates two different namespaces, vlsi.core and vlsi.inputs, and then two different keys, technology and supplies, which are set to the asap7 technology and 0.7 Volts supply voltage, respectively.

Further details about these keys and how they are manipulated is found in the Hammer IR and Meta Variables section.

## 1.1.2 Tech Plugins

A technology plugin consists of two or more files: a \*.tech.json and a defaults.yml.

The \*.tech.json contains pointers to relevant PDK files and fundamental technology constants. These values are not meant to be overriden, nor can they be for the time being.

defaults.yml sets default technology variables for Hammer to consume, which may be specific to this technology or generic to all. These values may be overriden by design-specific configurations. An example of this is shown in the open-source technology plugins in hammer/technology/, such as asap7, and how to setup a technology plugin is documented in more detail in the *Hammer Technology Plugins* section.

**Note:** Unless you are a UCB BAR or BWRC affiliate or have set up a 3-way technology NDA with us, we cannot share pre-built proprietary technology plugin repositories.

## 1.1.3 Tool Plugins

A Hammer tool plugin actually implements tool-specific steps of the VLSI flow in Hammer in a template-like fashion. The TCL commands input to the tool are created using technology and design settings provided by the designer.

There are currently three Hammer tool plugin repositories for commercial tools: hammer-cadence-plugins, hammer-synopsys-plugins, and hammer-mentor-plugins. In them are tool plugin implementations for actions including synthesis, place-and-route, DRC, LVS, and simulation. hammer-cadence-plugins and hammer-synopsys-plugins are publicly available; however, users must request access to hammer-mentor-plugins.

**Note:** If you are not a UCB BAR or BWRC affiliate and have access to Mentor Graphics (now Siemens) tools, please email hammer-plugins-access@lists.berkeley.edu with a request for access to the hammer-mentor-plugins repository. MAKE SURE TO INCLUDE YOUR GITHUB ID IN YOUR EMAIL AND YOUR ASSOCIATION TO SHOW YOU HAVE LICENSED ACCESS TO THE TOOLS. There will be no support guarantee for the plugin repositories, but users are encouraged to file issues and contribute patches where needed.

There are also a set of open-source tools (e.g. Yosys, OpenROAD, Magic, Netgen) provided in hammer/ under their respective actions.

These plugins implement many of the common steps of a modern physical design flow. However, a real chip flow will require many custom settings and steps that may not be generalizable across technology nodes. Because of this, Hammer has an "escape-hatch" mechanism, called a hook, that allows the designer to inject custom steps between the default steps provided by the CAD tool plugin. Hooks are python methods that emit TCL code and may be inserted before or after an existing step or replace the step entirely. This allows the designer to leverage the APIs built into Hammer while easily inserting custom steps into the flow. Hooks are discussed in more detail in the "Example usage" portion of the Hammer documentation.

5

## 1.1.4 Calling Hammer

To use Hammer on the command line, the designer will invoke the hammer-vlsi utility. This is calling the \_\_main\_\_() method of the CLIDriver class. An example invocation is below:

```

hammer-vlsi -e env.yml -p config.yml --obj_dir build par

```

Using hooks requires the designer to extend the CLIDriver class. A good example exists in the Chipyard repository (chipyard/vlsi/example-vlsi). This would change the invocation to something like the following:

```

example-vlsi -e env.yml -p config.yml --obj_dir build par

```

In both of these commands, an environment configuration is passed to Hammer using a -e flag, which in this case is env.yml. env.yml contains pointers to the required tool licenses and environment variables. These environment settings will not be propagated to the output configuration files after each action.

Any number of other YML or JSON files can then be passed in using the -p flag. In this case, there is only one, config.yml, and it needs to set all the required keys for the step of the flow being run. Passing in multiple files looks like -p config1.yml -p config2.yml. Refer to the *Hammer IR and Meta Variables* section for the implications of multiple config files.

--obj\_dir build designates what directory Hammer should use as a working directory. All default action run directories and output files will be placed here.

Finally, par designates that this is a place-and-route action.

In this case, Hammer will write outputs to the path \$PWD/build/par-rundir.

For the full list of Hammer command-line arguments, run *hammer-vlsi –help* or take a peek in the hammer/vlsi/cli\_driver.py file.

## 1.1.5 Summary

The software architecture as described above is shown in the diagram below, which is taken from the Hammer DAC paper.

1.1. Hammer Overview

## 1.2 Hammer Setup

Hammer depends on Python 3.9+.

The default technology, ASAP7, has some extra requirements. See its README for instructions.

## 1.2.1 User Setup

You can install Hammer from PyPI:

```

pip install hammer-vlsi

```

If you are using ASAP7, you need to install hammer-vlsi with the asap7 extra dependency (gdspy or gdstk). By default, gdspy is installed:

```

pip install hammer-vlsi[asap7]

```

If instead, you want to install gdstk:

```

pip install hammer-vlsi[asap7-gdstk]

```

After installation, verify that you can run the hammer-vlsi script from the command line.

```

hammer-vlsi -h

```

Note: certain tools and technologies will have additional system requirements. For example, LVS with Netgen requires Tcl/Tk 8.6, which is not installed for CentOS7/RHEL7 and below. Refer to each respective tool and technology's documentation for those requirements.

#### **Installing Hammer as a Source Dependency**

In some cases, it is useful to install Hammer as a source dependency. For instance, when developing tool or PDK plugins alongside a new feature or API changes in main Hammer, installing hammer as a source dependency will allow you to make changes in main hammer and see them reflected immediately when running code for your tool/PDK plugin.

## **From Another Poetry Project**

Hammer tool (e.g. hammer-cadence-plugins) and PDK plugin repositories are poetry projects (with a pyproject. toml in their root). To depend on Hammer as a source dependency, first clone Hammer somewhere on your disk. Then add this snippet to the tool/PDK plugin repo's pyproject.toml (and remove any PyPI dependency on Hammer):

```

[tool.poetry.dependencies]

#hammer-vlsi = "^1.0.0"

hammer-vlsi = {path = "path/to/hammer", extras = ["asap7"], develop = true}

```

Run poetry update and poetry install. Do not commit the changes to pyproject.toml or poetry.lock without first removing the source dependency. You only need to specify extras if you need the asap7 optional dependency (gdstk).

### From a Generic Python Project

Other repos, such as Chipyard, are not poetry projects, but still depend on Hammer. To use Hammer as a source dependency:

- 1. Remove the PyPI hammer-vlsi dependency from the project (e.g. by editing a conda env.yml file and rerunning dependency resolution)

- 2. Clone Hammer somewhere on your disk

- 3. Activate the virtualenv of the project (e.g. Chipyard)

- 4. Run pip install -e . from the root of Hammer within the project's virtualenv

#### 1.2.2 Developer Setup

1. Clone Hammer with git

```

git clone git@github.com:ucb-bar/hammer

cd hammer

```

2. Install poetry to manage the development virtualenv and dependencies

```

curl -sSL https://install.python-poetry.org | python3 -

```

3. Create a poetry-managed virtualenv using the dependencies from pyproject.toml

1.2. Hammer Setup 7

```

# create the virtualenv inside the project folder (in .venv)

poetry config virtualenvs.in-project true

poetry install

```

4. Activate the virtualenv. Within the virtualenv, Hammer is installed and you can access its scripts defined in pyproject.toml (in [tool.poetry.scripts])

```

poetry shell

hammer-vlsi -h

```

#### **Using PyCharm**

This project works out of the box with PyCharm. You should install the Pydantic plugin to enable autocomplete for Pydantic BaseModels.

#### **Unit Tests with pytest**

Within the poetry virtualenv, from the root of Hammer, run the tests (-v will print out each test name explicitly)

```

pytest tests/ -v

```

If you want to skip the single long running-test in test\_stackup.py:

```

pytest tests/ -m "not long" -v

```

If you want to run only a specific test use -k with a snippet of the test function you want to run:

```

pytest tests/ -k "lsf" -v

> tests/test_submit_command.py::TestSubmitCommand::test_lsf_submit[lsf] PASSED

```

By default, pytest will only display what a test prints to stdout if the test fails. To display stdout even for a passing test, use -rA:

### Type Checking with mypy

There is a small issue with the ruamel.yaml package typechecking which can be hacked around with:

```

touch .venv/lib/python3.10/site-packages/ruamel/py.typed

```

Inside your poetry virtualenv, from the root of Hammer, run:

```

mypy --namespace-packages --warn-unused-ignores -p hammer

Success: no issues found in 146 source files

mypy --namespace-packages --warn-unused-ignores tests

Success: no issues found in 25 source files

```

#### **Testing Different Python Versions with tox**

Hammer is supposed to work with Python 3.9+, so we run its unit tests on all supported Python versions using tox and pyenv.

1. Install pyenv

```

curl https://pyenv.run | bash

```

Restart your shell and run pyenv init (and follow any of its instructions). Then restart your shell again.

2. Install Python versions

See the .python-version file at the root of hammer and install those Python versions using pyenv.

```

pyenv install 3.9.13

pyenv install 3.10.6

```

Once the Python interpreters are installed, run pyenv versions from the root of hammer.

```

pyenv versions

system

* 3.9.13 (set by .../hammer/.python-version)

* 3.10.6 (set by .../hammer/.python-version)

```

3. From within your poetry virtualenv, run tox

```

tox

```

This will run the pytest unit tests using all the Python versions specified in pyproject.toml under the [tool.tox] key.

You can run tests only on a particular environment with -e

```

tox -e py39 # only run tests on Python 3.9

```

You can pass command line arguments to the pytest invocation within a tox virtualenv with --

```

tox -e py39 -- -k "lsf" -v

```

1.2. Hammer Setup 9

#### **Adding / Updating Dependencies**

To add a new Python (pip) dependency, modify pyproject.toml. If the dependency is only used for development, add it under the key [tool.poetry.dev-dependencies], otherwise add it under the key [tool.poetry.dependencies]. Then run poetry update and poetry install. The updated poetry.lock file should be committed to Hammer.

To update an existing dependency, modify pyproject.toml with the new version constraint. Run poetry update and poetry install and commit poetry.lock.

### **Building Documentation**

- Within your poetry virutualenv, cd doc

- · Modify any documentation files. You can migrate any rst file to Markdown if desired.

- Run sphinx-build . build

- The generated HTML files are placed in build/

- Open them in your browser firefox build/index.html

#### **Publishing**

Build a sdist and wheel (results are in dist):

```

poetry build

```

To publish on TestPyPI:

- 1. Create an account on TestPyPi

- 2. Note the source repository testpypi in pyproject.toml under the key [tool.poetry.source]

- To add another PyPI repository to poetry: poetry source add <source name> <source url>

- 3. Publish: poetry publish --repository testpypi -u <username> -p <password>

## 1.3 Migration Guide

Hammer's software infrastructure changed significantly for version 1.0.0. In order to use the latest version of Hammer, you will need to make changes to your existing tool/tech plugins, YML/JSON input files, and Python files that import Hammer.

This guide is relevant for both plugin developers and general users.

The documentation for old Hammer is cached here.

## 1.3.1 Selecting Plugins

Previously, tech and tool plugins were selected with a combination of tool name and relative plugin path:

```

vlsi.core.technology: <tech_name>

vlsi.core.technology_path: ["hammer-<tech_name>-plugin"]

vlsi.core.technology_path_meta: append

vlsi.core.synthesis_tool: <syn_tool_name>

vlsi.core.synthesis_tool_path: ["hammer-<vendor>-plugin/syn"]

vlsi.core.synthesis_tool_meta: append

```

Now, you simply need to specify the package name:

```

vlsi.core.technology: hammer.technology.<tech_name>

vlsi.core.synthesis_tool: hammer.synthesis.<syn_tool_name>

```

See the *Plugin File Structure* section below for details about plugin package structure.

#### 1.3.2 import Statements

When importing Hammer classes and/or methods, replace old statements:

```

import hammer_tech

from hammer_vlsi import HammerTool

```

with:

```

import hammer.tech

from hammer.vlsi import HammerTool

```

The rule of thumb is that underscores are replaced with periods. This will match the package directory structure under the hammer/ directory.

## 1.3.3 Technology JSON

Previously, the technology JSON file may have contained entries like this:

```

"gds map file": "path/to/layermap.file"

```

Now, keys must not contain spaces in line with JSON syntax:

```

"gds_map_file": "path/to/layermap.file"

```

The fields for installs and tarballs have also changed. Generally, path is now id and base var is now path to remove confusion. For example, previously (ASAP7 example for reference):

(continues on next page)

(continued from previous page)

is now:

## 1.3.4 Plugin File Structure

Plugins previously did not have a file structure requirement. For example, it could have looked like this:

```

mytech/

__init__.py

defaults.yml

mytech.tech.json

layer.map  # some tech-specific file

action/

action_tool/

__init__.py  # contains action_tool-specific hooks

tool.options  # some tech-specific file needed by this tool

```

The new structure must follow Python package convention, hence it will look as follows:

```

hammer/

mytech/

__init__.py

defaults.yml

mytech.tech.json

layer.map  # some tech-specific file

action/

```

(continues on next page)

(continued from previous page)

```

action_tool/

__init__.py # contains action_tool-specific hooks

tool.options # some tech-specific file needed for this tool

```

#### 1.3.5 Resource Files

Technology plugins will often provide special static files needed by tools, such as the layer.map file in the above example. If this file is already specified with the prependlocal meta action, the behavior will remain the same:

```

action.tool.layer_map: "layer.map"

action.tool.layer_map_meta: prependlocal

```

However, within a plugin, if you need to access to a specific file for a tool-specific hook, for example, in action/action\_tool/\_\_init\_\_.py, replace this:

```

with open(os.path.join(self.tool_dir, "tool.options")) as f:

```

With this and append Pathlib methods like read\_text() as required:

```

importlib.resources.files(self.package).joinpath("tool.options")

```

## 1.3.6 pyproject.toml

Plugins that are repositories separate from Hammer must now have a pyproject.toml file so that they become poetry projects. Refer to *From Another Poetry Project* for details.

### HAMMER TECHNOLOGY PLUGINS

This guide will walk you through how to set up a technology plugin to be used in Hammer.

You may use the included free ASAP7 PDK or the open-source Sky130 PDK plugins as reference when building your own technology plugin.

Technology plugins must be structured as Python packages underneath the hammer package. The package should contain an class object named tech to create an instance of the technology. This object should be a subclass of HammerTechnology.

Technology plugins must also have .tech.json and defaults.yml files. See the following sections for how to write them.

## 2.1 Hammer Technologies

Hammer currently has open-source technology plugins in the hammer/technology folder. Other proprietary technology plugins cannot be made public without 3-way NDAs or special agreements with their respective foundries.

The structure of each technology plugin package is as follows:

- hammer

- TECHNOLOGY NAME

- \* \_\_init\_\_.py contains the tech class object and methods for PDK installation/extraction and getting *hooks*.

- \* <name>.tech.json contains the static information about the technology. See the section *Hammer Tech JSON* for a guide.

- \* defaults.yml contains the default tech-specific *Hammer IR and Meta Variables*. See the section *Hammer Tech defaults.yml* for a guide.

- \* ACTION NAME

- · \_\_init\_\_.py (optional) can contain a technology's implementation of an action. Commonly, this is used for the SRAM compilation action.

- · TOOL NAME

- · \_\_init\_\_.py (optional) contains callable *hook* methods specific to the technology and tool, if there are too many to put in TECHNOLOGY\_NAME/\_\_init\_\_.py.

Resources that are needed may go in this directory structure where necessary.

## 2.1.1 HammerTechnology Class

The HammerTechnology class is the base class that all technology plugins should inherit from and is defined in hammer/tech/\_\_init\_\_.py. Particularly useful methods are:

- post\_install\_script: the plugin subclass should override this method to apply any non-default PDK installation steps or hotfixes in order to set up the technology libraries for use with Hammer.

- read\_libs: this is a particularly powerful method to read the libraries contained in the tech.json file and filter them using the filters also contained the same file. See the *Library Filters* section for details.

- get\_tech\_<action>\_hooks: these methods are necessary if tech—specific hooks are needed, and must return a list of hooks when a given tool name implementing the relevant action is called. Refer to the *Extending Hammer with Hooks* section for details about how to write hooks.

## 2.2 Hammer Tech JSON

The tech.json for a given technology sets up some general information about the install of the PDK, sets up DRC rule decks, sets up pointers to PDK files, and supplies technology stackup information. For the full schema of the tech JSON, please see the *Full Schema* section below, which is derived from the TechJSON Pydantic BaseModel in hammer/tech/\_\_init\_\_.py.

## 2.2.1 Technology Install

The user may supply the PDK to Hammer as an already extracted directory and/or as a tarball that Hammer can automatically extract. Setting technology.TECH\_NAME. install\_dir and/or tarball\_dir (key is setup in the defaults.yml) will fill in as the path prefix for paths supplied to PDK files in the rest of the tech.json. Below is an example of the installs and tarballs from the ASAP7 plugin.

```

"name": "ASAP7 Library",

"grid_unit": "0.001",

"time_unit": "1 ps".

"installs": [

{

"id": "$PDK".

"path": "technology.asap7.pdk_install_dir"

},

{

"id": "$STDCELLS",

"path": "technology.asap7.stdcell_install_dir"

}

],

"tarballs": [

"root": {

"id": "ASAP7_PDK_CalibreDeck.tar",

"path": "technology.asap7.tarball_dir"

"homepage": "http://asap.asu.edu/asap/".

"optional": true

}

],

```

The id field is used within the file listings further down in the file to prefix path, as shown in detail below. If the file listing begins with cache, then this denotes files that exist in the tech cache, which are generally placed there by the tech plugin's post-installation script (see ASAP7's post\_install\_script method). Finally, the encrypted Calibre decks are provided in a tarball and denoted as optional.

## 2.2.2 DRC/LVS Deck Setup

As many DRC & LVS decks for as many tools can be specified in the drc decks and lvs decks keys. Additional DRC/LVS commands can be appended to the generated run files by specifying raw text in the additional\_drc\_text and additional\_lvs\_text keys. Below is an example of an LVS deck from the ASAP7 plugin.

The file pointers, in this case, use the tarball prefix because Hammer will be extracting the rule deck directly from the ASAP7 tarball. The additional text is needed to tell Calibre that the dummy SRAM cells need to be filtered from the source netlist and boxed and filtered from the layout.

## 2.2.3 Library Setup

The libraries key also must be setup in the JSON plugin. This will tell Hammer where to find all of the relevant files for standard cells and other blocks for the VLSI flow. Below is an example of the start of the library setup and one entry from the ASAP7 plugin.

```

"libraries": [

"lef_file": "$STDCELLS/techlef_misc/asap7_tech_4x_201209.lef",

"provides": [

"lib_type": "technology"

}

]

},

"nldm_liberty_file": "$STDCELLS/LIB/NLDM/asap7sc7p5t_SIMPLE_RVT_TT_nldm_201020.lib.gz

"verilog_sim": "$STDCELLS/Verilog/asap7sc7p5t_SIMPLE_RVT_TT_201020.v",

"lef_file": "$STDCELLS/LEF/scaled/asap7sc7p5t_27_R_4x_201211.lef",

"spice_file": "$STDCELLS/CDL/LVS/asap7sc7p5t_27_R.cdl",

"gds_file": "$STDCELLS/GDS/asap7sc7p5t_27_R_201211.gds",

"qrc_techfile": "$STDCELLS/qrc/qrcTechFile_typ03_scaled4xV06".

"spice_model_file": {

"path": "$PDK/models/hspice/7nm_TT.pm"

},

```

(continues on next page)

(continued from previous page)

```

"corner": {

"nmos": "typical",

"pmos": "typical",

"temperature": "25 C"

},

"supplies": {

"VDD": "0.70 V",

"GND": "0 V"

},

"provides": [

{

"lib_type": "stdcell",

"vt": "RVT"

}

]

]

},

```

The file pointers, in this case, use the \$PDK and \$STDCELLS prefix as defined in the installs. The corner key tells Hammer what process and temperature corner that these files correspond to. The supplies key tells Hammer what the nominal supply for these cells are. The provides key has several sub-keys that tell Hammer what kind of library this is (examples include stdcell, fiducials, io pad cells, bump, and level shifters) and the threshold voltage flavor of the cells, if applicable. Adding the tech LEF for the technology with the lib\_type set as technology is necessary for place and route.

#### **Library Filters**

Library filters are defined in the LibraryFilter class in hammer/tech/\_\_init\_\_.py. These allow you to filter the entire set of libraries based on specific conditions, such as a file type or corner. Additional functions can be used to extract paths, strings, sort, and post-process the filtered libraries.

For a list of pre-built library filters, refer to the properties in the LibraryFilterHolder class in the same file, accessed as hammer.tech.filters.<filter\_method>

## 2.2.4 Stackup

The stackups sets up the important metal layer information for Hammer to use. Below is an example of one metal layer in the metals list from the ASAP7 example tech plugin.

```

{"name": "M3", "index": 3, "direction": "vertical", "min_width": 0.072, "pitch": 0.144,

→"offset": 0.0, "power_strap_widths_and_spacings": [{"width_at_least": 0.0, "min_spacing

→": 0.072}], "power_strap_width_table": [0.072, 0.36, 0.648, 0.936, 1.224, 1.512]}

```

All this information is typically taken from the tech LEF and can be automatically filled in with a script. The metal layer name and layer number is specified. direction specifies the preferred routing direction for the layer. min\_width and pitch specify the minimum width wire and the track pitch, respectively. power\_strap\_widths\_and\_spacings is a list of pairs that specify design rules relating to the widths of wires and minimum required spacing between them. This information is used by Hammer when drawing power straps to make sure it is conforming to some basic design rules.

#### 2.2.5 Sites

The sites field specifies the unit standard cell size of the technology for Hammer.

```

"sites": [

{"name": "asap7sc7p5t", "x": 0.216, "y": 1.08}

]

```

This is an example from the ASAP7 tech plugin in which the name parameter specifies the core site name used in the tech LEF, and the x and y parameters specify the width and height of the unit standard cell size, respectively.

## 2.2.6 Special Cells

The special\_cells field specifies a set of cells in the technology that have special functions. The example below shows a subset of the ASAP7 tech plugin for 2 types of cells: tapcell and stdfiller.

```

"special_cells": [

{"cell_type": "tapcell", "name": ["TAPCELL_ASAP7_75t_L"]},

{"cell_type": "stdfiller", "name": ["FILLER_ASAP7_75t_R", "FILLER_ASAP7_75t_L",

→"FILLER_ASAP7_75t_SL", "FILLER_ASAP7_75t_SRAM", "FILLERxp5_ASAP7_75t_R", "FILLERxp5_

→ASAP7_75t_L", "FILLERxp5_ASAP7_75t_SL", "FILLERxp5_ASAP7_75t_SRAM"]},

```

There are 8 cell\_type s supported: tiehicell, tielocell, tiehilocell, endcap, iofiller, stdfiller, decap, and tapcell. Depending on the tech/tool, some of these cell types can only have 1 cell in the name list.

There is an optional size list. For each element in its corresponding name list, a size (type: str) can be given. An example of how this is used is for decap cells, where each listed cell has a typical capacitance, which a place and route tool can then use to place decaps to hit a target total decapacitance value. After characterizing the ASAP7 decaps using Voltus, the nominal capacitance is filled into the size list:

### 2.2.7 Don't Use, Physical-Only Cells

The dont\_use\_list is used to denote cells that should be excluded due to things like bad timing models or layout. The physical\_only\_cells\_list is used to denote cells that contain only physical geometry, which means that they should be excluded from netlisting for simulation and LVS. Examples from the ASAP7 plugin are below:

```

"dont_use_list": [

"ICGx*DC*",

"AND4x1*",

```

(continues on next page)

(continued from previous page)

```

"SDFLx2*",

"AO21x1*",

"XOR2x2*",

"OAI31xp33*",

"OAI221xp5*",

"SDFLx3*",

"SDFLx1*",

"AOI211xp5*",

"OAI322xp33*",

"OR2x6*",

"A201A101Ixp25*",

"XNOR2x1*",

"OAI32xp33*",

"FAx1*",

"OAI21x1*"

"OAI31xp67*",

"OAI33xp33*",

"A021x2*",

"A0I32xp33*"

"physical_only_cells_list": [

"TAPCELL_ASAP7_75t_R", "TAPCELL_ASAP7_75t_L", "TAPCELL_ASAP7_75t_SL", "TAPCELL_ASAP7_

→75t_SRAM",

"TAPCELL_WITH_FILLER_ASAP7_75t_R", "TAPCELL_WITH_FILLER_ASAP7_75t_L", "TAPCELL_WITH_

→FILLER_ASAP7_75t_SL", "TAPCELL_WITH_FILLER_ASAP7_75t_SRAM",

"FILLER_ASAP7_75t_R", "FILLER_ASAP7_75t_L", "FILLER_ASAP7_75t_SL", "FILLER_ASAP7_75t_

→SRAM".

"FILLERxp5_ASAP7_75t_R", "FILLERxp5_ASAP7_75t_L", "FILLERxp5_ASAP7_75t_SL", "FILLERxp5_

→ASAP7_75t_SRAM"

],

```

## 2.2.8 Full Schema

Note that in the schema tables presented below, items with #/definitions/<class\_name> are defined in other schema tables. This is done for documentation clarity, but in your JSON file, those items would be hierarchically nested.

## **TechJSON**

| type                            | object        |           |  |  |  |

|---------------------------------|---------------|-----------|--|--|--|

| properties                      |               |           |  |  |  |

| • name                          | Name          | Name      |  |  |  |

|                                 | type          | string    |  |  |  |

| • grid_unit                     | Grid Unit     | Grid Unit |  |  |  |

|                                 | type          | string    |  |  |  |

| • time_unit                     | Time Unit     |           |  |  |  |

|                                 | type          | string    |  |  |  |

| <ul><li>shrink_factor</li></ul> | Shrink Factor |           |  |  |  |

|                                 | type          | string    |  |  |  |

continues on next page

Table 1 – continued from previous page

| <ul> <li>installs</li> </ul>     | • installs Installs             |                          |        |

|----------------------------------|---------------------------------|--------------------------|--------|

|                                  | type                            | array                    |        |

|                                  | items                           | #/definitions/PathPrefix |        |

| • libraries Libraries            |                                 |                          |        |

|                                  | type                            | array                    |        |

|                                  | items                           | #/definitions/Library    |        |

| • gds_map_file                   | Gds Map File                    | <u> </u>                 |        |

| 0 - 1-                           | type                            | string                   |        |

| • physi-                         | Physical Only Cells List        | 1 0                      |        |

| cal_only_cells_list              | type                            | array                    |        |

| _ •                              | items                           | type                     | string |

| dont_use_list                    | Dont Use List                   | 71                       |        |

|                                  | type                            | array                    |        |

|                                  | items                           | type                     | string |

| • drc_decks                      | Drc Decks                       | 71                       |        |

|                                  | type                            | array                    |        |

|                                  | items                           | #/definitions/DRCDeck    |        |

| • lvs_decks                      | Lvs Decks                       |                          |        |

|                                  | type                            | array                    |        |

|                                  | items                           | #/definitions/LVSDeck    |        |

| • tarballs                       | Tarballs                        |                          |        |

|                                  | type                            | array                    |        |

|                                  | items                           | #/definitions/Tarball    |        |

| • sites                          | Sites                           |                          |        |

|                                  | type                            | array                    |        |

|                                  | items                           | #/definitions/Site       |        |

| <ul> <li>stackups</li> </ul>     | Stackups                        |                          |        |

|                                  | type                            | array                    |        |

|                                  | items                           | #/definitions/Stackup    |        |

| • special_cells                  | Special Cells                   |                          |        |

|                                  | type                            | array                    |        |

|                                  | items #/definitions/SpecialCell |                          |        |

| <ul><li>extra_prefixes</li></ul> | Extra Prefixes                  |                          |        |

|                                  | type                            | e array                  |        |

|                                  | items                           | #/definitions/PathPrefix |        |

| additional_lvs_text              |                                 |                          |        |

|                                  | type                            | string                   |        |

| additional_drc_text              |                                 |                          |        |

|                                  | type                            | string                   |        |

## **PathPrefix**

| A path prefix which defines an identifier and its corresponding path. |                                        |                |  |  |  |  |

|-----------------------------------------------------------------------|----------------------------------------|----------------|--|--|--|--|

| Example: A PathPrefix(id = "Alib", 1                                  | path = "/scratch/projectA/mylib") maps | the identifier |  |  |  |  |

| 'Alib' to the path '/scratch/projectA/mylib'                          |                                        |                |  |  |  |  |

| type                                                                  | object                                 |                |  |  |  |  |

| properties                                                            | properties                             |                |  |  |  |  |

| • id                                                                  | Id                                     | Id             |  |  |  |  |

|                                                                       | type string                            |                |  |  |  |  |

| • path                                                                | Path                                   |                |  |  |  |  |

|                                                                       | type                                   | string         |  |  |  |  |

## Corner

| type          | object      |             |  |  |

|---------------|-------------|-------------|--|--|

| properties    |             |             |  |  |

| • nmos        | Nmos        | Nmos        |  |  |

|               | type        | string      |  |  |

| • pmos        | Pmos        | Pmos        |  |  |

|               | type        | string      |  |  |

| • temperature | Temperature | Temperature |  |  |

|               | type        | string      |  |  |

## MinMaxCap

| type       | object  |         |  |  |

|------------|---------|---------|--|--|

| properties |         |         |  |  |

| • max_cap  | Max Cap | Max Cap |  |  |

|            | type    | string  |  |  |

| • min_cap  | Min Cap |         |  |  |

|            | type    | string  |  |  |

## Provide

| type       | object   |          |  |  |

|------------|----------|----------|--|--|

| properties |          |          |  |  |

| • lib_type | Lib Type | Lib Type |  |  |

|            | type     | string   |  |  |

| • vt       | Vt       |          |  |  |

|            | type     | string   |  |  |

## Supplies

| type       | object |        |  |

|------------|--------|--------|--|

| properties |        |        |  |

| • GND      | Gnd    |        |  |

|            | type   | string |  |

| • VDD      | Vdd    |        |  |

|            | type   | string |  |

## SpiceModelFile

| type         | object     |        |  |

|--------------|------------|--------|--|

| properties   |            |        |  |

| • path       | Path       |        |  |

|              | type       | string |  |

| • lib_corner | Lib Corner | ·      |  |

|              | type       | string |  |

## Library

| object                  |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

| Name                    |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

| type                    | string                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |

| Ccs Liberty File        |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

| type                    | string                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |

| Ccs Library File        |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

| type                    | string                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |

| Ecsm Liberty File       |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

| type                    | string                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |

| Ecsm Library File       |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

| type                    | string                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |

| #/definitions/Corner    |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

|                         |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

|                         |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

| #/definitions/MinMaxCap |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

|                         |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

|                         |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

| *                       |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

|                         | string                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |

|                         |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

| type                    | string                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |

| Spice File              |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

| type                    | string                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |

| Gds File                |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |

| type                    | string                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |

|                         | Name type Ccs Liberty File type Ccs Library File type Ecsm Liberty File type Ecsm Library File type #/definitions/Corner  #/definitions/MinMaxCap  Lef File type Klayout Techfile type Spice File type Gds File | Name type string  Ccs Liberty File type string  Ccs Library File type string  Ecsm Liberty File type string  Ecsm Library File type string  #/definitions/Corner  #/definitions/MinMaxCap  Lef File type string  Klayout Techfile type string  Spice File type string  Gds File |

continues on next page

Table 2 – continued from previous page

| <ul><li>milkyway_lib_in_dir</li></ul>  | Milkyway Lib In Dir          |                       |  |

|----------------------------------------|------------------------------|-----------------------|--|

|                                        | type                         | string                |  |

| milkyway_techfile                      | Milkyway Techfile            |                       |  |

|                                        | type                         | string                |  |

| nldm_liberty_file                      | Nldm Liberty File            |                       |  |

|                                        | type                         | string                |  |

| <ul> <li>nldm_library_file</li> </ul>  | Nldm Library File            | •                     |  |

|                                        | type                         | string                |  |

| openaccess_techfile                    | Openaccess Techfile          |                       |  |

|                                        | type                         | string                |  |

| • provides                             | Provides                     |                       |  |

|                                        | type                         | array                 |  |

|                                        | items                        | #/definitions/Provide |  |

| • qrc_techfile                         | Qrc Techfile                 |                       |  |

|                                        | type                         | string                |  |

| • supplies                             | #/definitions/Supplies       |                       |  |

| • tluplus_files                        | #/definitions/MinMaxCap      |                       |  |

| • tluplus_map_file                     | Tluplus Map File             |                       |  |

|                                        | type                         | string                |  |

| • verilog_sim                          | Verilog Sim                  |                       |  |

| -                                      | type                         | string                |  |

| • verilog_synth                        | Verilog Synth                |                       |  |

|                                        | type                         | string                |  |

|                                        | #/definitions/SpiceModelFile |                       |  |

| • spice_model_file                     | -                            |                       |  |

| <ul> <li>power_grid_library</li> </ul> | Power Grid Library           |                       |  |

|                                        | type                         | string                |  |

| • extra prefixes                       |                              |                       |  |

| <ul> <li>extra_prefixes</li> </ul>     | Extra Prefixes               |                       |  |

| • extra_prefixes                       | Extra Prefixes type          | array                 |  |

## **DRCDeck**

| type        | object    |        |  |

|-------------|-----------|--------|--|

| properties  |           |        |  |

| • tool_name | Tool Name |        |  |

|             | type      | string |  |

| deck_name   | Deck Name | ·      |  |

|             | type      | string |  |

| • path      | Path      | ·      |  |

|             | type      | string |  |

## **LVSDeck**

| type        | object    |           |  |

|-------------|-----------|-----------|--|

| properties  | ·         |           |  |

| • tool_name | Tool Name |           |  |

|             | type      | string    |  |

| deck_name   | Deck Name | Deck Name |  |

|             | type      | string    |  |

| • path      | Path      |           |  |

|             | type      | string    |  |

### Tarball

| type                         | object                   |          |  |

|------------------------------|--------------------------|----------|--|

| properties                   |                          |          |  |

| • root                       | #/definitions/PathPrefix |          |  |

| • homepage                   | Homepage                 | Homepage |  |

|                              | type                     | string   |  |

| <ul> <li>optional</li> </ul> | Optional                 | Optional |  |

|                              | type                     | boolean  |  |

|                              | default                  | False    |  |

## Site

| A standard cell site, which is the min | imum unit of x and y dimensions a stan   | dard cell can have.                 |  |

|----------------------------------------|------------------------------------------|-------------------------------------|--|

| name: The name of this site (often so  | mething like "core") as defined in the t | ech and standard cell LEFs x: The x |  |

| dimension y: The y dimension           |                                          |                                     |  |

| type                                   | object                                   |                                     |  |

| properties                             |                                          |                                     |  |

| • name                                 | Name                                     |                                     |  |

|                                        | type                                     | string                              |  |

| • x                                    | X                                        |                                     |  |

|                                        | type                                     | number                              |  |

| • y                                    | Y                                        |                                     |  |

|                                        | type                                     | number                              |  |

## RoutingDirection

| Represents a preferred routing direction for a metal layer. Note that this represents a <i>preferred</i> direction, not a DRC |                                      |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|

| rule.                                                                                                                         |                                      |  |  |

| type                                                                                                                          | string                               |  |  |

| enum                                                                                                                          | vertical, horizontal, redistribution |  |  |

### WidthSpacingTuple

A tuple of wire width limit and spacing for generating a piecewise linear rule for spacing based on wire width. width\_at\_least: Any wires larger than this must obey the minSpacing rule. min\_spacing: The minimum spacing for this bin.

If a wire is wider than multiple entries, the worst-case (larger) minSpacing wins.

| -                                  | , C , 1        | C      |

|------------------------------------|----------------|--------|

| type                               | object         |        |

| properties                         |                |        |

| <ul> <li>width_at_least</li> </ul> | Width At Least |        |

|                                    | type           | number |

| • min_spacing                      | Min Spacing    |        |

|                                    | type           | number |

#### Metal

A metal layer and some basic info about it.

name: Metal layer name (e.g. M1, M2). index: The order in the stackup (lower is closer to the substrate). direction: The preferred routing direction of this metal layer, or

RoutingDirection.Redistribution for non-routing top-level redistribution metals like Aluminium. min\_width: The minimum wire width for this layer. max\_width: The maximum wire width for this layer. pitch: The minimum cross-mask pitch for this layer (NOT same-mask pitch

for multiple-patterned layers). Width of routing grid for a given layer. To route denser wires on chip, multiple masks are required. During fabrication, the masks are applied separately with some spatial offsets to achieve denser line patterning. For more information on multiple-patterning, check https://en.wikipedia.org/wiki/Multiple\_patterning

offset: The routing track offset from the origin for the first track in this layer.

(0 = first track is on an axis).

power\_strap\_widths\_and\_spacings: A list of WidthSpacingTuples that specify the minimum

spacing rules for an infinitely long wire of variying width.

power\_strap\_width\_table: A list of allowed metal widths in the technology.

Widths smaller than the last number must be quantized to a value in the table.

grid\_unit: The fixed-point decimal value of a minimum grid unit (e.g. 1nm = 0.001).

For most technologies, this comes from the technology plugin and is the same for all layers.

|                         | •                           | rogy pragm and is the same is | · ·· ·· ·· ·· · · · · · · · · · · · · |

|-------------------------|-----------------------------|-------------------------------|---------------------------------------|

| type                    | object                      |                               |                                       |

| properties              |                             |                               |                                       |

| • name                  | Name                        |                               |                                       |

|                         | type                        | string                        |                                       |

| <ul><li>index</li></ul> | Index                       |                               |                                       |

|                         | type                        | integer                       |                                       |

| • direction             | #/definitions/RoutingDirect | tion                          |                                       |

| • min_width             | Min Width                   |                               |                                       |

|                         | type                        | number                        |                                       |

| max_width               | Max Width                   |                               |                                       |